1、引言

數字射頻存儲器(DRFM)具有對射頻和微波信號的存儲及再現能力,已發展成為現代電子戰系統和儀器測試系統的重要組成部分。作為DRFM 的核心部分,超高速ADC,DAC 的性能直接決定了它處理模擬信號的能力。但是,由于半導體工藝及器件性能的限制,高采樣率、高分辨率的ADC 及DAC 難以實現。由于相位數字化比傳統的幅度數字化有多種優點,且采用相位量化可降低對上述電路的要求,所以含相位體制ADC 及DAC 的DRFM 系統得到廣泛應用[1~4 ]。本文利用GaAs MESFET 全離子注入非自對準常規工藝設計了用于3bit 相位體制DRFM 系統的單片超高速相位體制ADC。測試結果表明,電路可在2GHz 時鐘速率下完成采樣、量化,達到1.2Gbp s 的輸出碼流速率,其瞬時帶寬可達150MHz,具備±0.22LSB 的相位精度。

2、電路設計

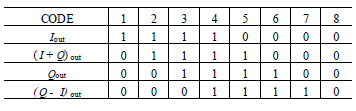

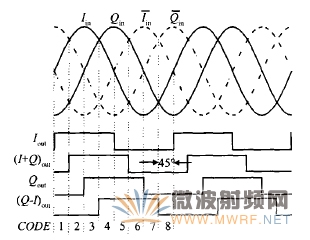

3bit 相位體制ADC 的量化對象是輸入信號的相位量,基本功能是將輸入的兩路正交模擬信號轉換為四路含相位信息的數字信號。輸出信號是占空比為1:1、頻率與輸入正交信號同頻率的方波信號,但每相鄰兩路之間的相位差為45°[3 ]。3bit 相位體制ADC 的輸入輸出時序關系及真值表分別如圖1、表1 所示。所以,3bit 相位體制ADC 的輸出信號每周期含8 個相位態,電路的轉換速率為輸入模擬信號頻率的8 倍。

表1、輸出真值表

圖1、輸入輸出時序圖

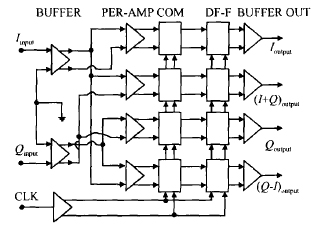

根據3bit 相位體制ADC 的工作原理,設計電路框圖如圖2 所示。

圖2、3bit 相位體制ADC 電路框圖

3bit 相位體制ADC 主要由五部分電路組成:(1)輸入緩沖級。本級電路將輸入的單端模擬正交信號變換為ADC 內部所需的互補信號,并具有一定的放大作用。此外,該級電路還包括將外部的單端時鐘信號變換為內部其他各級電路所需的互補時鐘信號。(2)預放大級。本級電路根據3bit 相位量化的原理對模擬正交信號及其互補信號按照一定規則兩兩組合,進行差分放大。(3)比較級。本級電路在時鐘作用下,利用正反饋原理對比較器輸入端的模擬信號進行取樣、量化。(4)觸發鎖存級。本級電路在時鐘的精確控制下,對前級比較級輸出的量化數字值進行觸發鎖存。(5)輸出緩沖級。目的是為了在高速數字傳輸時能足以驅動ADC 后級的50Ω 負載。電路設計時,已將輸入、輸出端口設計為片內50Ω 匹配,便于高速測試及應用。

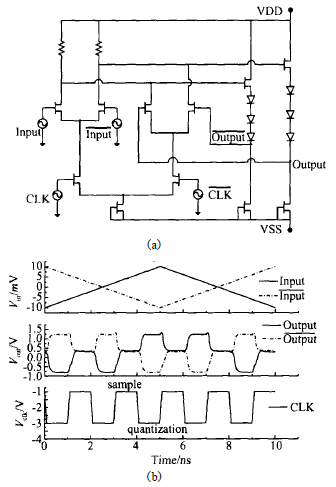

上述各級電路中,最為關鍵的部分是比較級電路。通過它將模擬信號采樣、量化為數字信號,本級輸出數字信號的質量將影響后級觸發鎖存級能否可靠工作。所以,它的性能直接決定了整個ADC 電路的工作速度。為了獲得高增益及良好的輸入動態范圍,采用栓鎖再生比較器,利用其正反饋的工作原理達到高的采樣、量化速度,且對小的輸入信號仍然能夠正確工作,為后級的觸發鎖存級提供足夠的量化數字電平[5 ]。栓鎖再生比較器的電原理圖如圖3(a)所示。圖3(b)為其在20mVpp 輸入信號、500MHz 時鐘作用下的仿真工作特性。

圖3、(a)栓鎖再生比較器;(b)比較器仿真結果

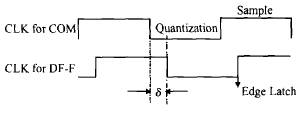

由圖3 可知,該比較器在時鐘的高電平作用下對外部輸入信號進行取樣,直至時鐘的高電平結束。這一過程中,比較器負載電阻端的電平及比較器的輸出端電平均跟隨外部輸入信號而變。到達時鐘的下降沿時,比較器利用正反饋作用立刻將時鐘高電平最后時刻取樣的外部信號進行量化,使比較器的輸出端強置于穩態的高、低電平。因此,比較器的負載電阻、輸入取樣對管的柵寬及正反饋量化對管的柵寬都需要仔細設計,以達到高增益、高輸出量化擺幅。比較器的后級采用下降沿D 型觸發器,利用與比較器相同的時鐘信號進行觸發鎖存。為了對比較器的量化輸出穩態值進行可靠觸發鎖存,需要精細設計整個ADC 電路的時鐘分布。最終版圖布局時恰當安排各級版圖位置,使到達觸發鎖存級的時鐘信號稍稍滯后于比較器級(如δ),即可用同一時鐘可靠同步整個ADC 電路。最終電路的具體時序安排如圖4 所示。

圖4、ADC 各級電路時鐘時序分布

由于相位體制ADC 的量化對象是信號的相位量,因此芯片版圖設計時將片內互補時鐘單元置于整個電路版圖的中心,保證電路內部同一級4 個通道的時鐘信號邊沿相差不大。此外,還要盡量保證各通道內部信號所走路徑長度一致。

由于本電路最終將采用全離子注入非自對準常規工藝,而ADC 又對器件的離散非常敏感,所以結合實際工藝情況,利用蒙特卡羅分析,計算了ADC電路對器件閾值電壓離散的敏感度,進而分析電路的成品率。通過不斷改進各級電路中器件的柵寬比例使得最終ADC 電路在現有工藝水平下能夠達到80 %以上的成品率,至此電路設計完畢。

3、工藝實現

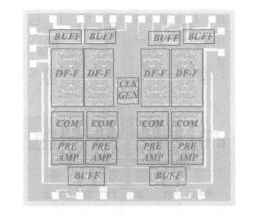

電路采用南京電子器件研究所標準GaAsΦ76mm 全離子注入工藝實現,器件均為耗盡型器件,為非自對準常規工藝。工藝流程簡介如下:N- 有源區采用大面積Si 離子注入形成,注入能量為60keV,劑量為4.3 ×1012 cm-2;N+ 區采用Si 離子選擇雙注入形成,注入能量分別為120,60keV,劑量均為3 ×1013cm-2;源漏歐姆接觸金屬采用Au/ Ge/ Ni 金屬系統,柵采用常規Ti/ Pt/ Au 柵。整個流程應用金屬剝離工藝,電路用Si3N4 介質實現兩層金屬布線隔離。嚴格控制柵挖槽工藝,調整器件的閾值電壓到目標電壓-1.3V。最終得到的芯片實際照片如圖5 所示,芯片尺寸為2mm ×2mm,各功能模塊均以框圖標示。

4、電路測試

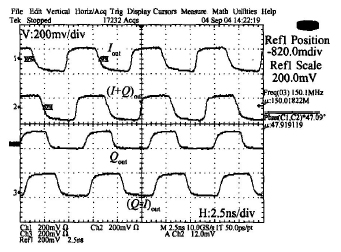

設計測試專用的測試盒及高速PCB 板,芯片直接裝配到測試底座上,通過金絲鍵合至PCB 上的傳輸線。由于電路本身含有驅動50Ω 負載的輸出緩沖驅動電路,因此,測試過程中電路存在比較大的高速開關電流。為了保證在這種電流急速開關變化下的信號完整性,需要對所有的直流饋線交流旁路,旁路電容采用1μf 和100pf 的貼片電容,以此來穩定直流饋電的電壓穩定。由于電路的量化對象是相位量,所以需要嚴格避免輸入輸出電纜給各通道所引入的額外相位誤差。以每個通道輸出信號經過各自高低電平的50 %點為基準進行相位差統計。圖6 為高頻150MHz 輸入模擬正交信號、2GHz 時鐘速率下的測試結果,ADC 的輸出碼流速率均為1.2Gbp s。由圖可見,電路各通道的相位關系正確,輸出幅度在50Ω 負載上均有180mVpp 的擺幅。

圖5、3bit 相位體制ADC 芯片照片

圖6、150MHz 輸入、2GHz 時鐘速率下的輸出波形

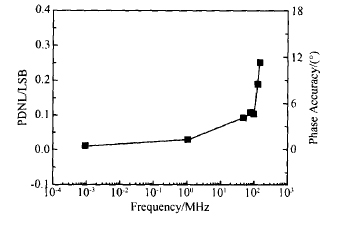

相位量化ADC 最關鍵的參數是相位精度隨工作頻率的變化情況,它決定了ADC 電路的瞬時工作帶寬。在某一頻率f 下,Pha(i)代表實際第i 個碼元所對應的相位量,那么該頻率下的相位精度PA(f)可表示為:

PA(f)= max(abs(Pha(i)- 45)) i = 1,2 ?,8

同傳統的幅度ADC,也可以用線性度隨工作頻率的變化描述電路的頻域性能。定義PDNL(f)代表該頻率下的微分線性度,則:

PDNL(f)= PA(f)/ 45

圖7 是該電路的微分非線性誤差及相位精度隨頻率的變化特性。

圖7、PDNL 及相位精度的動態性能

由圖7 測試結果可知,如果定義10°相位誤差(對應±0.22LSB)為界,那么該電路具有接近150MHz的帶寬,ADC 的輸出碼流速率可達1.2Gbps。以上測試結果均在2GHz 時鐘速率下測得。

5、結論

本文詳細討論、分析了用于3bit 相位體制DRFM 系統的3bit 相位體制ADC 的設計過程。利用南京電子器件研究所標準GaAs Φ76mm 全離子注入工藝,采用全耗盡非自對準MESFET 器件加工實現了3bit 超高速相位體制ADC。測試結果表明,電路可在2GHz 時鐘速率下完成采樣、量化,達到1.2Gbp s 的輸出碼流速率,其瞬時帶寬可達150MHz,具備±0.22LSB 的相位精度。經進一步改進后可應用于3bit 相位體制DRFM 系統中。

粵公網安備 44030902003195號

粵公網安備 44030902003195號