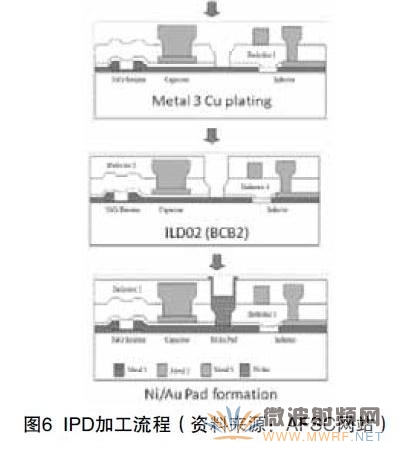

IMEC的薄膜技術(shù)也是采用電鍍銅做為連接線路,BCB做為介電層,Ni/Au層做為最終連接面金屬,使用多達(dá)4層的金屬層。其IPD結(jié)構(gòu)如圖3所示。

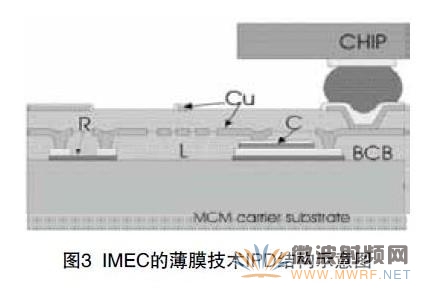

(3)Dai Nippon

Dai Nippon發(fā)展的IPD電阻以Ti/Cr為主,電容采用陽極氧化形成Ta2O5的制程,電感設(shè)計為有微帶線和螺旋電感,線路以銅為主。如圖4所示。

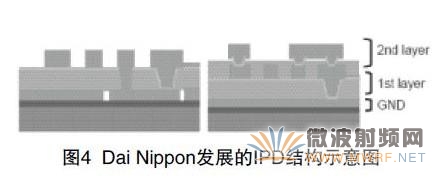

(4)SyChip

SyChip發(fā)展的IPD以TaSi為電阻材料,電容的介電材料為Si3N4,上電極為Al,下電極為TaSi,電感和線路材料都采用鋁。如圖5所示。

有一些公司正在采用MEMS工藝來發(fā)展IPD,如PHS MEMS公司,據(jù)該公司解釋,制造MEMS元件的方法基本上來自IC產(chǎn)業(yè)。同時,一些老牌公司在開發(fā)相關(guān)技術(shù)的同時,也通過收購等手段獲得市場和技術(shù),如村田(Murata)就收購了SyChip公司,期望通過該次收購擴(kuò)張其在射頻應(yīng)用市場的份額。

4、薄膜集成無源元件技術(shù)的結(jié)構(gòu)與制程

薄膜制程與厚膜制程最大的差異就在于產(chǎn)生的膜厚,一般所謂的厚膜厚度多在5μm ~ 10μm以上,而薄膜制程產(chǎn)生的膜厚約在0.01μm ~ 1μm之間。

如果利用薄膜制程同時形成電阻、電容、電感的元件,需要用不同的制程與材料來制作。薄膜技術(shù)應(yīng)用在半導(dǎo)體集成電路制程,技術(shù)發(fā)展已經(jīng)相當(dāng)成熟,所以在進(jìn)行制程整合時,只需注意不同元件間材料的相容性,即可達(dá)成制程的設(shè)計。

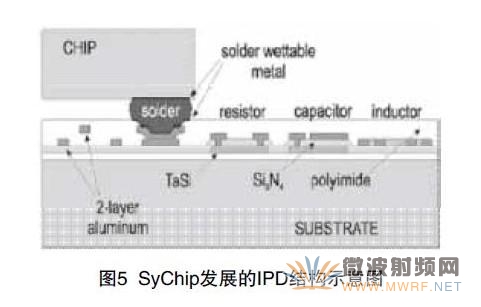

整體而言,薄膜IPD集成無源元件,可因不同的產(chǎn)品應(yīng)用,制作在不同的基板上,基板可選擇硅晶片、氧化鋁陶瓷基板、玻璃基板,薄膜IPD集成無源元件技術(shù)可以集成薄膜電阻、電容和電感于一體,其制程技術(shù)開發(fā),包括:微影加工技術(shù)、薄膜沉積加工技術(shù)、蝕刻加工技術(shù)、電鍍加工技術(shù)、無電極電鍍加工技術(shù),整個加工流程如圖6所示。除了無源元件的整合,在硅晶片上也可以結(jié)合主動元件的制程,將無源元件與主動元件電路整合以達(dá)到多功能化的需求。下面就薄膜電阻、電容和電感的加工分別作簡單介紹。

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號