數(shù)字上變頻/下變頻(DUC/DDC)是數(shù)字中頻設計的重要組成部分,其功能是將基帶信號經(jīng)過內(nèi)插濾波后變到中頻的頻率,或者將中頻的信號經(jīng)過抽取濾波后降到基帶的頻率上。本文的主要目的就是介紹多天線多載波數(shù)字上下變頻的FPGA實現(xiàn)方法,以及Altera提供的一種數(shù)字信號處理的工具,DSP BUILDER。

DUC/DDC的實現(xiàn)架構

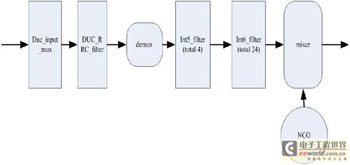

以TD-SCDMA的DUC/DDC為例,基帶頻率1.28MHz, 4天線9載波,60倍上變頻,30倍下變頻的情況下,DUC的架構如圖1所示

圖1,DUC的架構圖。

首先4天線9載波,每個載波分IQ兩路,一共4×9×2=72個通道,這72個通道的數(shù)據(jù)先由duc_input_mux模塊復合到一路上,輸入到duc_rrc_filter上,做2倍內(nèi)插以及根升余弦濾波,這是一個121階的濾波器;輸出結果分成4路,分別送到4個int5_filter(61階)模塊中,做5倍內(nèi)插及補償濾波;這4個濾波器的輸出再被分成24路,送進int6_filter(41階)模塊中,做6倍內(nèi)插及濾波;其結果進入混頻模塊mixer,與NCO產(chǎn)生的中頻信號混頻后作為最終結果輸出。

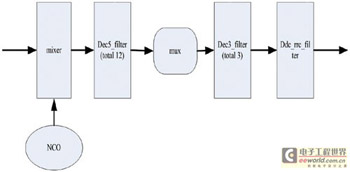

圖2 ,DDC的架構如圖

DDC的架構如圖2所示,對DDC而言,入口是4個天線下來的數(shù)據(jù),經(jīng)過混頻器區(qū)分到不同頻點上,再由抽取濾波器dec5_filter(41階)做5倍抽取以及濾波;結果復合到3路上,由3個dec3_filter(61階)做3倍抽取濾波;最后由ddc_rrc_filter(121階)做兩倍抽取以及濾波。

我們可以看出,對DUC/DDC而言,主要模塊是FIR濾波器、混頻器、以及數(shù)控振蕩器NCO,復用解復用邏輯占用的資源非常小。濾波器占用了大部分資源,包括查找表、寄存器、RAM、乘法器。因此優(yōu)化濾波器設計,以節(jié)省資源,用盡量小規(guī)模的FPGA實現(xiàn)更多通道的數(shù)字上下變頻,成為主要的實現(xiàn)難度。

DSP-BUILDER簡介

DSP-BUILDER是Altera Corporation的一種設計工具,可以把它看作MATLAB SIMULINK和FPGA實現(xiàn)軟件QUARTUS II之間的一個橋梁。簡單來說,在SIMULINK環(huán)境下,調(diào)用DSP-BUILDER提供的庫元件,搭建的這么一個數(shù)學模型系統(tǒng),不僅可以在MATLAB中仿真,還能直接生成一個ALTERA FPGA的工程,綜合布局布線后上硬件驗證。這里有一點是要強調(diào)的,只能調(diào)用DSP-BUILDER中的庫元件才能生成一個可以綜合實現(xiàn)的工程。

1、 DSP-BUILDER8.0以后的版本,提供了一個新的ADVANCED BLOCK的特性,用這個新特性產(chǎn)生的FIR濾波器,較之以往的版本,在資源優(yōu)化方面有了巨大的改進。

2、 自動插入流水。只需要設置好相應參數(shù),如時鐘頻率,目標器件,復用倍數(shù)等,它會在使用盡量少的資源并且滿足時序的情況下,自動判斷是否加入PIPELINE。

3、 系統(tǒng)層面的設計。它生成的所有模塊,包括FIR濾波器,都有一組系統(tǒng)接口,可以通過不同地址對內(nèi)部寄存器,如系數(shù)等,進行訪問。

4、 自動實現(xiàn)資源復用。在時鐘復用關系確定后,它能自動實現(xiàn)資源復用,使設計者從繁瑣的優(yōu)化工作中解放出來,專注于系統(tǒng)層面的設計。

整個設計的FPGA實現(xiàn)的資源以及功耗

這個4天線9載波的設計在Altera Corporation 的3SE80F1152I3上實現(xiàn),工作頻率為180倍基帶速率時鐘,即230MHz。內(nèi)核靜態(tài)功耗為734.58mW,內(nèi)核動態(tài)功耗為2705.63mW,IO功耗為236.82mW,全部功耗加起來為3677.04mW。

3SE80是ALTERA CORPORATION的65nm產(chǎn)品STRATIX III中的一款。這一系列產(chǎn)品在設計過程中考慮了很多功耗優(yōu)化的因素,因此功耗特性比較好。比如內(nèi)核電壓,它是0.9V/1.1V可選,上述設計用的是1.1V電壓,如果用0.9V的話,功耗還可以再降低30%。但有一點需要客戶注意,使用0.9V電壓的話,整個設計的時序會降低15%左右。

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號