設計包含了估算與優化。估算可以對多個可能的實現選擇做出比較。另外,優化可以自動完成,或者可以在各種抽象水平上,用工具輔助完成。Apache/Ansys應用工程總監Arvind Shanmugavel認為,只有當擁有了一個完整設計和一組正確的矢量時,功率估算才是一種精確的科學。在未完成設計以前,根據定義,所有事物都是一種即將在設計中發生的估計。在設計早期的功率預算階段,應著眼于大的和相對的變化,而不是絕對的值。Atrenta公司的工程總監Venki Venkatesh認為,可以預期在RTL(寄存器傳輸級)到硅片之間有20%的偏差,而從門到硅片有10%的偏差。

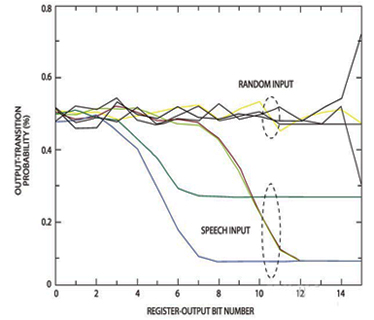

如果某個工具表示, 一種可能的方案會較另一種方案消耗更少的總能量,則這種概述一定是正確的;否則,工具就可能促使選擇了次級的方案。與面積和性能不同,功率是矢量相關的,因此可能需要運行多次仿真,來獲得有關設計活動的一種典型性樣本。例如,考慮兩種選擇,一種是為音頻處理器加隨機數據,一種是用更多的典型語音數據。圖2給出了一個有限脈沖響應濾波器中幾個寄存器的轉換動作(參考文獻1)。對于一個不會破壞數據相關性的架構,語音數據開關電容的次數要比隨機輸入數據少80%。由于這些臨時的相關性,運行順序可能造成切換動作的巨大差異。

圖2,對于一個不會破壞數據相關性的架構,語音數據開關電容的次數要比隨機輸入數據少80%。由于這些臨時的相關性,運行順序可能造成切換動作的巨大差異。

不過, 有些公司認為可以用統計方法獲得近似值, 即采用來自計數器或其它可識別邏輯片的預期活動。現在, 功耗優化有很多種方式,大多數為RTL或以下。Shanmugavel稱,時鐘門控是盡量減少動態功耗的常見技術。切斷某個電路的時鐘,可阻止一個設計中時鐘或寄存器的切換動作。另一種技術是采用電壓島,它降低了設計的工作電壓,從而使開關元件的動態功耗前后比值為電壓前后比值的平方。設計者將電壓島用于芯片的某些區域,這些區域的性能與速度不是關鍵,這樣可以節省功耗。

DVFS(動態電壓/頻率縮放)是迄今最為復雜的動態功率控制技術。這種方法會根據負載的需求,改變有效工作電壓和頻率。在高負載情況下,電壓與頻率處于額定狀態,芯片或設備為滿負荷工作。在低負載情況下,電壓或頻率縮減,以低速工作,從而獲得了較低的動態功耗。設計者可通過軟硬件方案的組合,實現這種技術。

片芯上的穩壓器滿足了對多種動態與靜態功率的需求。各IC通常有片外的穩壓模塊,可提供動態狀態下需要的電壓與電流。但是,設計者越來越多地采用片芯上的穩壓器,因為電壓域的數量在增加,這些電壓域更快響應需求的要求也在增加。

堆疊IC間的相互通信盡量減少了信號互連,它是低功耗設計中一種新興的趨勢。Apache的Shanmugavel認為,制造商一般是將處理器和存儲器堆疊在一個硅插入層上, 用TSV(硅通孔)做連接。這些插入層提供了片芯之間的低電容信號互連,從而降低了I/O的動態功耗。隨著3D IC的成本開始下降,以及設計者對于熱效應有了更多的理解,整個行業都將出現一個向3D IC的遷移。

要盡量減少靜態功耗, 設計者可以采用電源門控方法,為一個待機狀態的設備節省最多的泄漏功。關閉功能單位的時鐘可降低動態功耗,但單元仍然有泄漏功耗。設計者必須在設計實現以前,了解有關電源門控的幾個折中問題。

減少泄漏功耗的一種最古老技術是用高閾值電壓門代換標稱閾值電壓的門。在CMOS中,亞閾值泄漏與閾值電壓成反比。較高閾值電壓器件的泄漏包絡低于較小閾值電壓的器件,但付出的代價是較大的延遲。設計者必須做一個仔細的權衡分析,才能用此技術獲得最佳的減少泄漏效果。

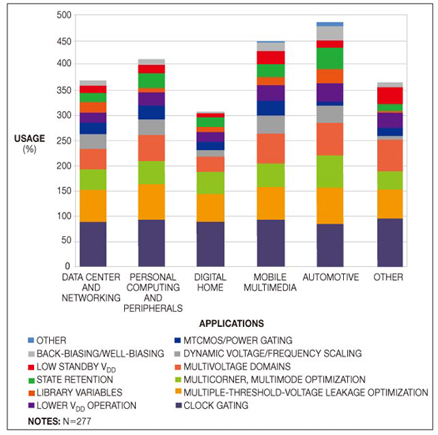

另外一種降低靜態功耗的方法是有源反偏,它是增加CMOS門中基材結點的偏置電壓,從而降低泄漏電流。這種偏置技術根本上是在待機模式期間增加一個單元或整個芯片的閾值電壓,從而減少泄漏功耗。為了感受一下這些技術的采納率,Synopsys通過自己的一個“全球用戶調查”,收集了用戶數據(圖3)。

粵公網安備 44030902003195號

粵公網安備 44030902003195號