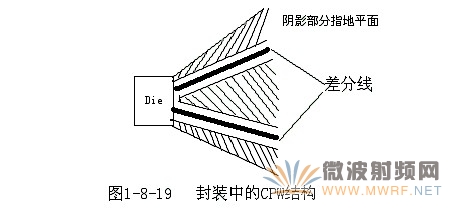

差分走線也可以走在不同的信號層中,但一般不建議這種走法,因為不同的層產生的諸如阻抗、過孔的差別會破壞差模傳輸的效果,引入共模噪聲。此外,如果相鄰兩層耦合不夠緊密的話,會降低差分走線抵抗噪聲的能力,但如果能保持和周圍走線適當的間距,串擾就不是個問題。在一般頻率(GHz以下),EMI也不會是很嚴重的問題,實驗表明,相距500Mils的差分走線,在3米之外的輻射能量衰減已經達到60dB,足以滿足FCC的電磁輻射標準,所以設計者根本不用過分擔心差分線耦合不夠而造成電磁不兼容問題。

3. 蛇形線

蛇形線是Layout中經常使用的一類走線方式。其主要目的就是為了調節(jié)延時,滿足系統(tǒng)時序設計要求。設計者首先要有這樣的認識:蛇形線會破壞信號質量,改變傳輸延時,布線時要盡量避免使用。但實際設計中,為了保證信號有足夠的保持時間,或者減小同組信號之間的時間偏移,往往不得不故意進行繞線。

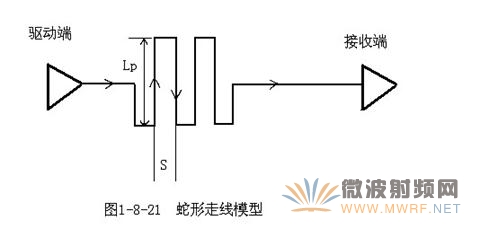

那么,蛇形線對信號傳輸有什么影響呢?走線時要注意些什么呢?其中最關鍵的兩個參數就是平行耦合長度(Lp)和耦合距離(S),如圖1-8-21所示。很明顯,信號在蛇形走線上傳輸時,相互平行的線段之間會發(fā)生耦合,呈差模形式,S越小,Lp越大,則耦合程度也越大。可能會導致傳輸延時減小,以及由于串擾而大大降低信號的質量,其機理可以參考第三章對共模和差模串擾的分析。

下面是給Layout工程師處理蛇形線時的幾點建議:

1. 盡量增加平行線段的距離(S),至少大于3H,H指信號走線到參考平面的距離。通俗的說就是繞大彎走線,只要S足夠大,就幾乎能完全避免相互的耦合效應。

2. 減小耦合長度Lp,當兩倍的Lp延時接近或超過信號上升時間時,產生的串擾將達到飽和。

3. 帶狀線(Strip-Line)或者埋式微帶線(Embedded Micro-strip)的蛇形線引起的信號傳輸延時小于微帶走線(Micro-strip)。理論上,帶狀線不會因為差模串擾影響傳輸速率。

4. 高速以及對時序要求較為嚴格的信號線,盡量不要走蛇形線,尤其不能在小范圍內蜿蜒走線。

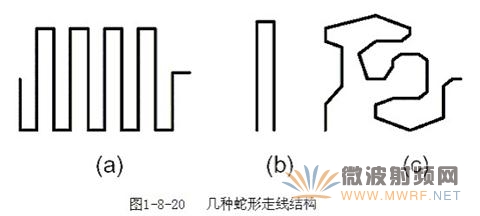

5. 可以經常采用任意角度的蛇形走線,如圖1-8-20中的C結構,能有效的減少相互間的耦合。

6. 高速PCB設計中,蛇形線沒有所謂濾波或抗干擾的能力,只可能降低信號質量,所以只作時序匹配之用而無其它目的。

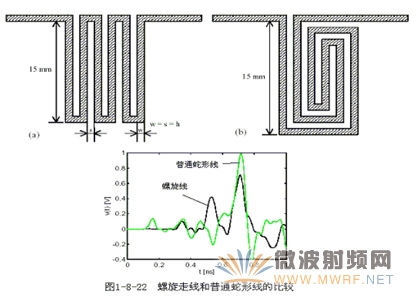

7. 有時可以考慮螺旋走線的方式進行繞線,仿真表明,其效果要優(yōu)于正常的蛇形走線。

粵公網安備 44030902003195號

粵公網安備 44030902003195號