有些設計師有時會忽略設計出來的芯片是否能夠順利的被制造出來應用到產品中,他們往往更關注指標是否達到,先考慮設計再考慮測試,但隨著電路復雜程度的提高,這種方法既費時又費力,并且往往造成制造過程中的一些不可預見的測試問題。解決芯片測試的根本方法是在芯片設計時就充分考慮到測試的要求,即在設計階段就開始考慮如何對電路進行測試,并將一些可測性技術引入到芯片中,以降低測試方法的復雜性,這就是可測性設計(DFT,Design For Testability )。

可測性設計是在滿足芯片正常功能的基礎上,通過有效地加入測試電路,來降低芯片的測試難度,降低測試成本。同時,可測性并不是指產品可測或不可測,而是度量產品測試難易度的概念,因此一般來說,一切考慮了測試要求的設計,或者說一切能使測試生成和故障診斷變得比較容易的設計都可稱為可測性設計。

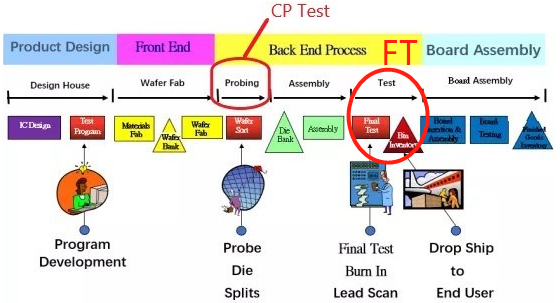

1、CP測試和FT測試

芯片在生產過程中主要有兩次測試:CP測試(晶圓測試,Chip Probing)和FT測試(Final Test )。CP是對wafer進行測試,檢查fab廠制造的工藝水平

FT是對package進行測試,檢查封裝廠的制造水平

圖1.1 CP和FT測試在芯片制程中的位置

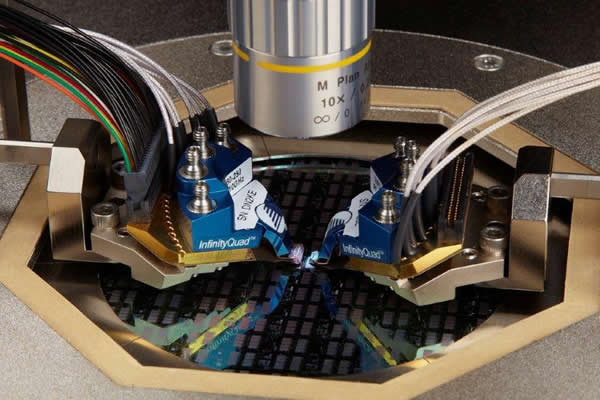

第一次測試是在晶圓加工完成后,測試設備通過探針壓到芯片的焊盤(Bonding Pad)上,這叫做CP測試,CP測試一般只做簡單的測試,比如電氣連通性、電流測試和一些專門為工藝調試的電路參數測試等,如果結果與預計的相同則為合格,否則判定測試失敗,在失敗芯片上打上標記,往后就不做這些故障芯片的封裝和后續加工。

第二次測試是在封裝完成后,測試儀通過測試程序完成對芯片的FT測試,這一次的測試一般要求更加嚴格,要盡可能地檢測出有故障的芯片。芯片的FT測試的內容不光是檢測故障,還有許多方面需要測試,如功耗、電流、可靠性、工作頻率、能夠工作的環境溫度等。如果檢測出芯片有故障,不能通過測試,那么要根據情況做故障分析或失效分析。一般來說故障分析會占用大量的人力、物力和時間,所以一般只是在非常必要的情況下才會去做。對于代工廠來說一些基本的工藝參數如果與預期不一致的話,是必須做分析的,并且要調整生產線,直到工藝穩定,總體偏差越小越好。對于設計者來說,實驗性的芯片如果有故障,要多花時間和精力進行詳細的調試和分析,找到問題的所在,修改設計直到正確無誤。

2、可測性設計的目標

對電路進行可測性設計主要為了達到以下目標:

(1)減少冗余邏輯:冗余邏輯會增加測試生成的復雜性;(2)增加電路的可控制性和可觀測性:增加電路的可控性和可觀性是提高電路可測性的根本措施;

(3)為了測試而附加的電路對原來電路的性能影響盡可能小:可測性設計都會增加額外的測試電路,通常會使芯片面積增加,影響電路本來的性能;

(4)使測試向量的生成更容易:簡單有效的測試向量可以提高測試效率,減少測試成本,尤其是時間成本;

(5)提高測試集的測試質量:提高故障覆蓋率、減少測試向量、減少測試時間等。

良好的可測性電路應具有以下特征:

(1)電路容易置于理想的初始狀態;(2)電路的任意內部狀態很容易通過對原始輸入施加測試圖形來控制;

(3)通過電路的原始輸出或專門的測試點,電路內部的狀態可以唯一確認。

3、可測性設計方法

對于頻率較高的射頻芯片來說,一般只能通過增加芯片內部的控制點和觀察點來實現可測性設計,即在電路設計和版圖設計的時候,通過增加可探測的電路支點和物理觸點來實現芯片可測量,有針對性的對電路的易失效點進行測試測量。

DFT設計針對的對象是什么?

DFT需要處理芯片上所有DC、AC測試需求,即DFT需要涵蓋以下電路模塊的測量:片上存儲器

模擬模塊 (如鎖相環,LDO,IDV等)

系統控制模塊(如串并轉換、休眠電路、看門狗電路等)

電源管理模塊(如DCDC、LDO等)

寄存器(如ROM、SPI協議等)

放大器(如MOS管、FET管)

DFT基本參與了所有的芯片功能,需要提供芯片初始化時FUSE的管理;需要設計協調時鐘、復位,放大器的DC/IV曲線;除此之外,芯片中功能模塊的每一個寄存器都是DFT設計的工作對象。

DFT應該參與到芯片支撐的哪些步驟中?

在芯片的整個制程中,都應該有DFT參與的痕跡,也就是DFT至少應該參與到以下過程中:在產品立項階段就應該定義好DFT的架構

在芯片design階段應該DFT的邏輯和驗證

在封裝階段應保證封裝芯片能夠完全的表現芯片的功能、邏輯、性能

在可靠性試驗階段應該做到DFT能夠實時監控

在交付階段保證DFT能夠為客戶提供幫助

在產品生命周期中DFT能夠監控壽命

粵公網安備 44030902003195號

粵公網安備 44030902003195號