1. 介紹

NI VST FPGA軟件包含多層代碼,提供了從底層控制到高層抽取的一切,擁有RF信號分析儀和RF信號發生器的功能。底層組件實現了具體硬件的標準功能,包括信號校準、前端控制,以及基于記錄的采集和生成,被稱為儀器設計庫。這些庫提供了互相匹配的主機和FPGA代碼對,并且可以聚集以構建完整的硬件設計。LabVIEW項目樣例包含了基于儀器設計庫的相關主機和FPGA代碼,提供了開發各種應用所需要的模板。另外,NI-RFSA和NI-RFSG儀器驅動還支持VST儀器驅動FPGA擴展,使VST FPGA源代碼完美適合具體應用。

2. 儀器設計庫

NI提供矢量信號收發器所用的多種儀器設計庫。如上文所述,這些儀器設計庫存在于用戶和生產廠商的關于主機端和FPGA的代碼中,,實現了儀器的常見功能。表2列出了一些頂層儀器設計庫及其功能。

表1. NI VST所用頂層儀器設計庫。

ni.com/vst/getting-started/zhs/所列軟件安裝了這些儀器設計庫,在硬盤的c:\Program Files\National Instruments\LabVIEW [version]\instr.lb\位置。這些庫具有顏色和諧的粗邊框,與其他VI明顯有別。

圖1:儀器設計庫具有顏色和諧的粗邊框,此獨特圖標使其與其他VI相區別

另外,這些庫在默認情況下處于鎖定狀態,用戶在修改內容之前,需要先通過會話框將VI解鎖。下文所述是使用這些儀器設計庫的詳細信息,適用于任何更改。

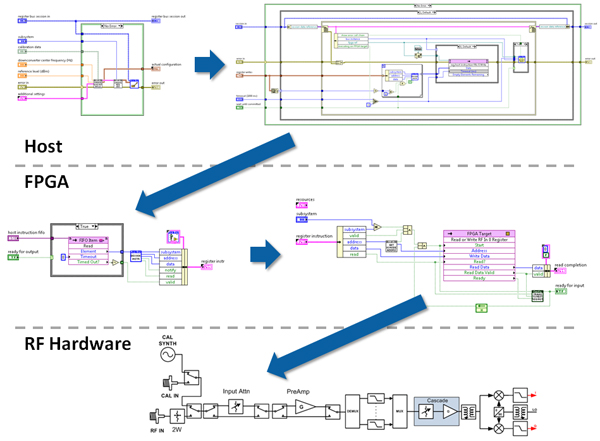

在給定儀器設計庫的主機與FPGA之間交換數據可采用多種機制。所有采用LabVIEW RIO架構和LabVIEW FPGA的NI產品均使用NI-RIO驅動,此驅動提供了單點方式的、存儲器映射、基于寄存器的主機至FPGA以及FPGA至主機通信,還有從主機至FPGA以及FPGA至主機的多點連續DMA FIFO。這些都是功能強大的數據交換機制,實現主機與FPGA之間的有效通信不需要了解或者只要些許了解底層總線架構。

儀器設計庫的一個常見要求是:主機代碼需要將大量的設置下載到設備中,例如要對與FPGA相連接的芯片寄存器進行編程,或者更新設置組,例如FPGA上的濾波器抽頭。由于一些儀器設計庫要求采用此策略,并且設備的DMA通道數目有限,所以這些庫可能需要共享一個FIFO,從而需要在主機端和FPGA端增加額外的邏輯來實現。另外,對于大數據集來說,此類通信一般為單向,但是可能也需要提供從FPGA至主機的某種單點確認,例如確認所有設置均已成功應用等等。所有這些概念組成為一個單獨概念,稱為寄存器總線,并為一些儀器設計庫所采用。

寄存器總線使用一個主機到FPGA端的DMA FIFO來下載設置,以及一些寄存器/NI-RIO控制器和指示器,用于握手,將單點數據返回主機,或者發出信號,確認已下載設置中的指令已經應用。

圖2. 寄存器總線是基于NI-RIO DMA、控制器和指示器構建的輕質協議,實現了大量設置組至FPGA的高效下載,這是給定儀器設計庫的主機與FPGA側之間的常見要求。

粵公網安備 44030902003195號

粵公網安備 44030902003195號