NI矢量信號收發(fā)器的FPGA編程

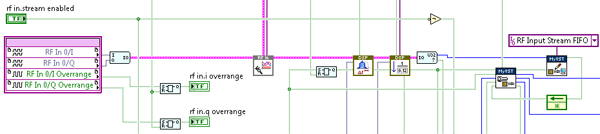

兩個項目樣例FPGA VI之間的主要區(qū)別是:VST Streaming項目樣例使用輕質(zhì)機(jī)制完成與主機(jī)之間的數(shù)據(jù)收發(fā)。它采用簡單的流控制器,支持基本觸發(fā)、連續(xù)和間斷流,以及溢出和下溢檢測。這些控制器中斷信號源與目的地之間的2線握手信號,有效地選通數(shù)據(jù)流。控制器不支持全4線握手方案,該方案能夠調(diào)整上游節(jié)點(diǎn)或者被下游節(jié)點(diǎn)所調(diào)整;因此,系統(tǒng)特性化以及確保這些流控制器控制的所有FIFO均能夠以要求的速率產(chǎn)生或消耗數(shù)據(jù)就落到了程序員的肩上。在VST Streaming項目樣例中通過簡單的更改默認(rèn)情況下完成與主機(jī)之間的數(shù)據(jù)收發(fā)的FIFO,可以支持?jǐn)?shù)據(jù)流傳輸?shù)絍ST FPGA上的其他位置以進(jìn)行進(jìn)一步處理,或者通過PXI Express背板,利用P2P傳輸至其他模塊。

圖14.FPGA流控制器和FIFO封裝實(shí)現(xiàn)基本流控制,并且能夠輕松改變數(shù)據(jù)流的源及目的地路線。

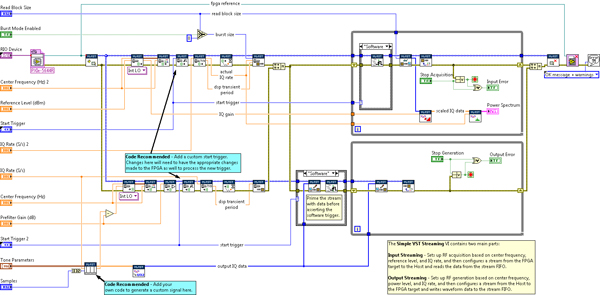

現(xiàn)在來看VST Streaming項目樣例的主機(jī)端,雖然機(jī)制與Simple VSA/VSG不同,也存在類似于儀器設(shè)計庫主機(jī)組件的集成,。VST Streaming項目樣例不使用LabVIEW類,而是將功能簡單地集成到子VI中,并將會話傳遞至子VI之間的寄存器總線。此寄存器總線會話還包含有FPGA VI 引用,因此所有這些子VI不僅能夠訪問寄存器總線通信策略,而且還可以訪問NI-RIO FIFO和控制器。另外,不存在獨(dú)立的數(shù)據(jù)采集和生成會話;所有VI均使用同一會話。

圖15.VST Streaming項目樣例主機(jī)接口具有一個基于寄存器總線的會話線,用于采集和生成subVI。在邏輯上,此樣例將采集和生成分組成為獨(dú)立的行,以方便閱讀。

VST Streaming項目樣例提供兩個主機(jī)樣例。較簡單的一個樣例把從VST處采集得到的增多的或者連續(xù)的波形數(shù)據(jù)傳輸至VST進(jìn)行生成,。比較高級的樣例說明了多個VST的MIMO同步。

圖16.這些樣例說明了VST Streaming項目樣例的主機(jī)接口

4. 儀器驅(qū)動FPGA擴(kuò)展

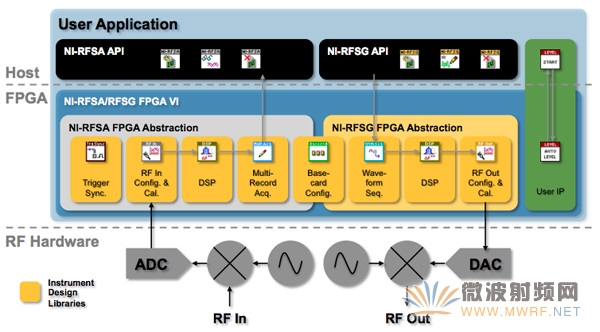

儀器驅(qū)動FPGA擴(kuò)展提供了一種兼容NI-RFSA和NI-RFSG儀器驅(qū)動的VST FPGA編程方法。FPGA上的抽取層實(shí)現(xiàn)了所需要的儀器驅(qū)動功能,同時提供接口以改善具體應(yīng)用的FPGA。雖然不像儀器設(shè)計庫的直接編程那樣靈活,然而儀器驅(qū)動FPGA擴(kuò)展支持的修改類型與標(biāo)準(zhǔn)信號分析儀和信號發(fā)生器的基于記錄的采集和生成模式相一致。

圖17. 儀器驅(qū)動FPGA擴(kuò)展架構(gòu)包含VST儀器設(shè)計庫,并且增加了一個抽取層以保護(hù)組件。用戶IP不在此代碼中,由主機(jī)進(jìn)行控制,并且不受預(yù)編譯封閉源NI-RFSA和NI-RFSG的影響

5. 大型FPGA開發(fā)考慮事項

The Virtex-6 LX195T FPGA on the NI PXIe-5644R and the NI PXIe-5645R is a large FPGA, though the full suite of instrument design libraries consumes a considerable fraction of the available resources. As such, compilation times can take 5 hours or more when using the NI LabVIEW FPGA Compile Cloud Service, depending on the complexity and resource utilization of the FPGA design. Furthermore, FPGA compilation is a non-deterministic process, and as a design consumes more FPGA resources, the repeatable compilation success rate drops below 100%. For such designs, initiating multiple compiles in parallel can help to ensure a successful compilation in approximately the same time as a single compilation. Table 3. provides some estimates for the different FPGA designs discussed in this paper.

| FPGA設(shè)計 | 近似編譯時間 | 近似編譯成功率 | LUT占用率 | 觸發(fā)器占用率 | DSP片占用率 | 塊RAM占用率 |

| VST Streaming項目范例 | 4 小時 | 90% | 27% | 30% | 31% | 20% |

| Simple VSA/VSG項目范例 | 5 小時 | 80% | 50% | 49% | 31% | 39% |

| 儀器驅(qū)動FPGA擴(kuò)展 | 6 小時 | 75% | 67% | 62% | 31% | 45% |

表3. 各種VST FPGA設(shè)計的編譯時間、成功率和FPGA占用率。

粵公網(wǎng)安備 44030902003195號

粵公網(wǎng)安備 44030902003195號